The AERIS-10 project has developed a completely open modular radar station (radar), which can be used as a platform for conducting experiments c phased antenna arrays, pulse compression, Doppler signal processingand target tracking. Complete schematics, PCB layouts, parts lists (BOMs), Gerber files for board manufacturing, 3D printing layouts and descriptions of hardware units in Verilog/VHDL are distributed under the CERN-OHL-P license (CERN Open Hardware License). The firmware code for the STM32 microcontroller, auxiliary utilities in C and a graphical interface in Python are supplied under the MIT license.

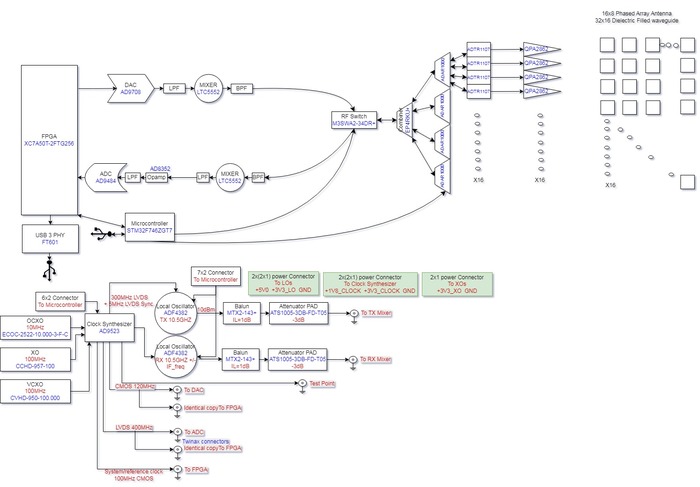

Two versions of the phased array radar have been prepared – AERIS-10N (Nexus) and AERIS-10E (Extended). Both options use the 10.5 GHz frequency and use pulsed linear frequency modulation (LFM). The differences come down to the radiation power (1Wx16 and 10Wx16), as well as the use of an array of planar antennas8x16 and an array of slot emitters in a dielectrically filled 32×16 waveguide, providing a range of up to 3 km and 20 km, respectively.

The system is modular with separate boards for power management, frequency generation and RF units. The XC7A100T FPGA is used to process signals, compress pulses, calculate object velocity using Doppler fast Fourier transform, eliminate stationary objects (MTI), and ensure a constant false alarm rate (CFAR). Operation control and configuration of peripheral devices is carried out using the STM32F746xx microcontroller.